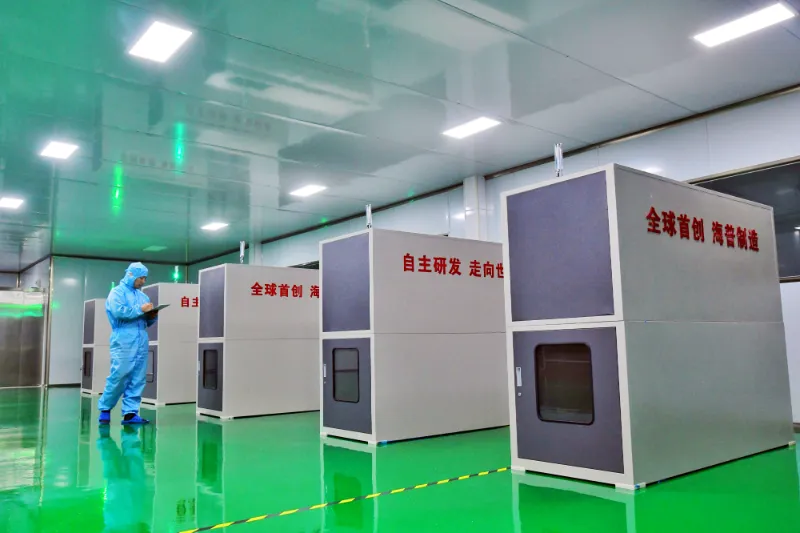

- Physical Protection and Reliability Enhancement

- Protection from Mechanical Damage: The packaging shell protects the chip from external impacts, vibrations, and bending.

- Environmental Protection: It shields the chip from moisture, dust, and corrosive gases (such as sulfur compounds).

- Temperature Shock Resistance: By selecting materials with matching thermal coefficients (e.g., low CTE substrates), the packaging reduces thermal stress and protects the chip from temperature shocks.

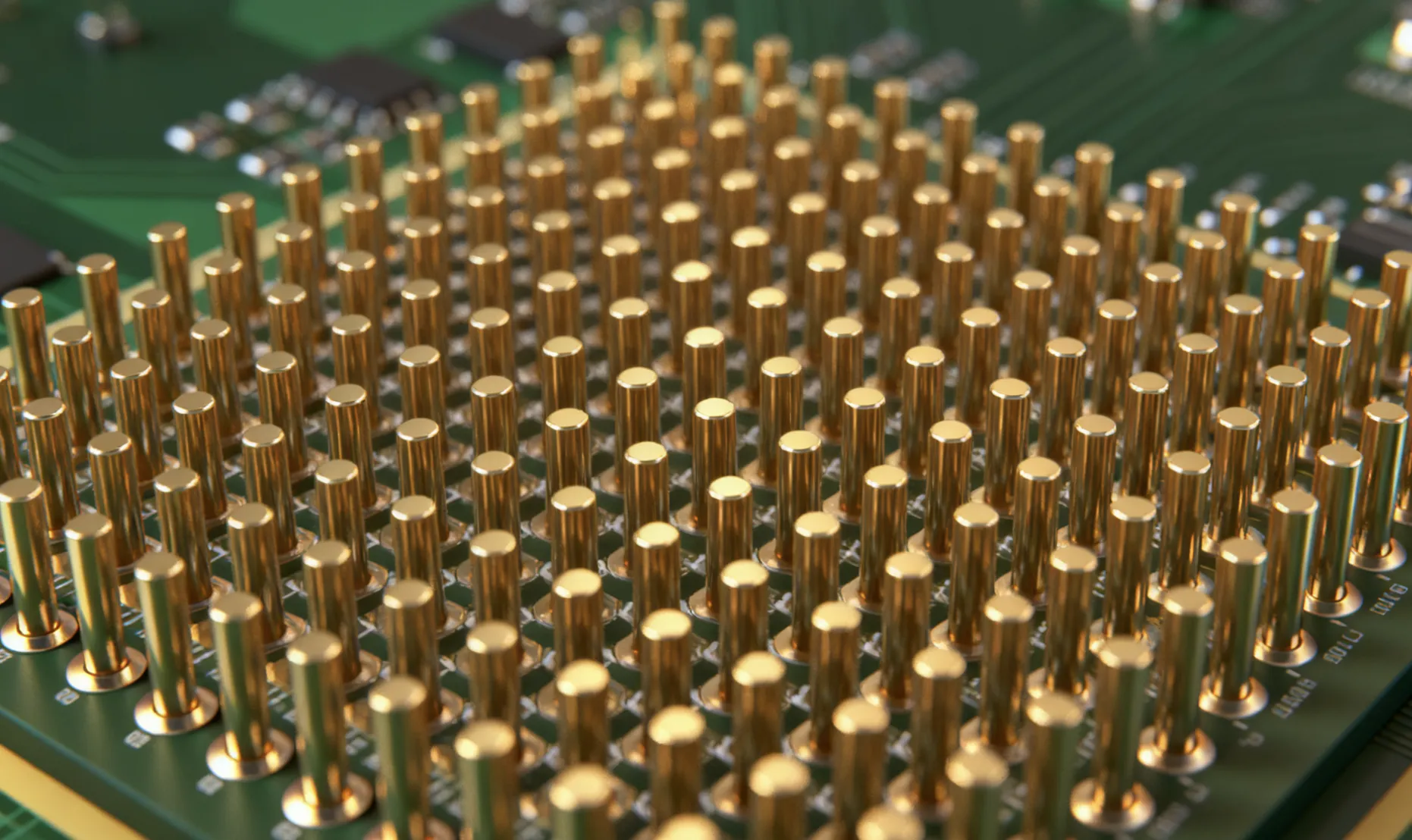

- Electrical Connection and Signal Integrity

- Power Delivery: The pins or solder balls supply power to the chip (e.g., high current for CPUs).

- Signal Transmission: High-frequency signals require impedance control (e.g., microbumps in Flip-Chip packages reduce path length, ensuring faster and more efficient signal transmission).

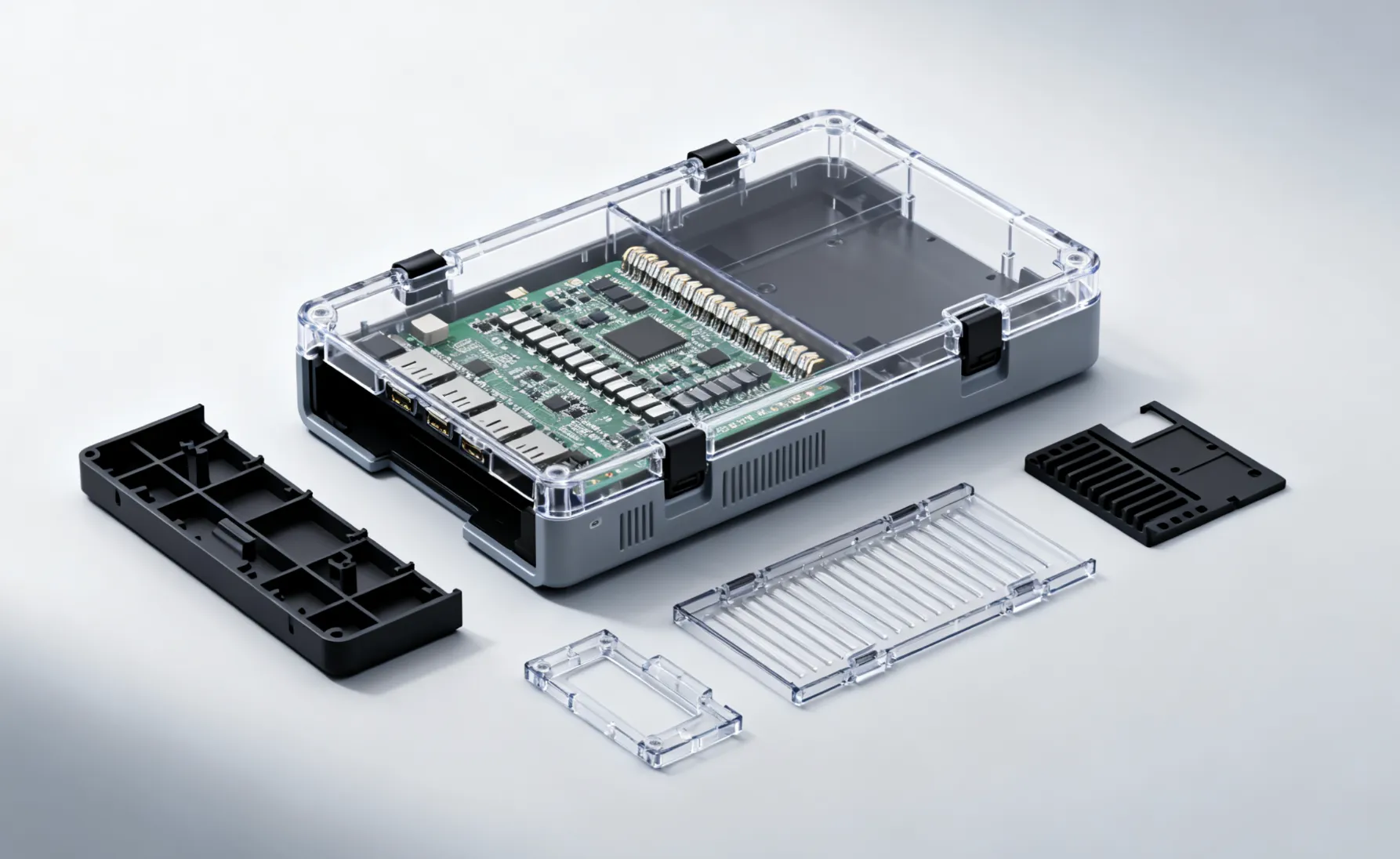

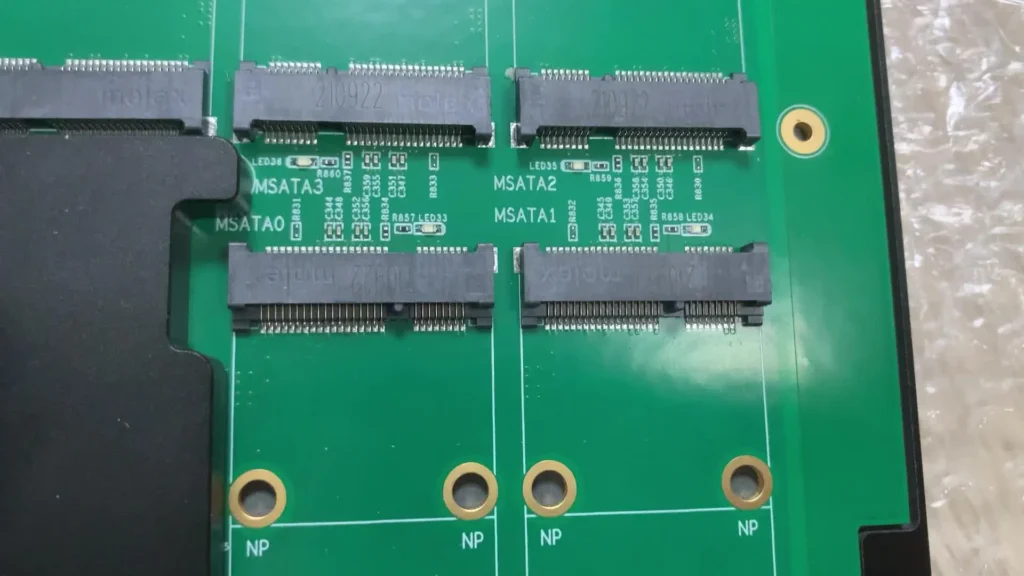

- Miniaturization and Integration

- High-Density Interconnects: Advanced packaging technologies (e.g., Fan-Out for Apple A-series chips) enable smaller sizes with more I/O connections.

- Heterogeneous Integration: Different functional chips (e.g., CPU + memory) can be integrated within a single package, enhancing functionality and reducing space.

- 3D Stacking: Technologies like HBM (High Bandwidth Memory) use TSV (Through-Silicon Vias) for vertical stacking, improving performance while reducing the overall size.

This optimized packaging process enhances the overall chip performance, reduces footprint, and improves reliability in a variety of electronic applications.